LilyGo T-Beam Supreme is a development board based on the ESP32S3 microcontroller using XTENSA architecture.

This board features a maximum CPU frequency of 240 MHz and 16MB flash memory.

About LilyGo T-Beam Supreme

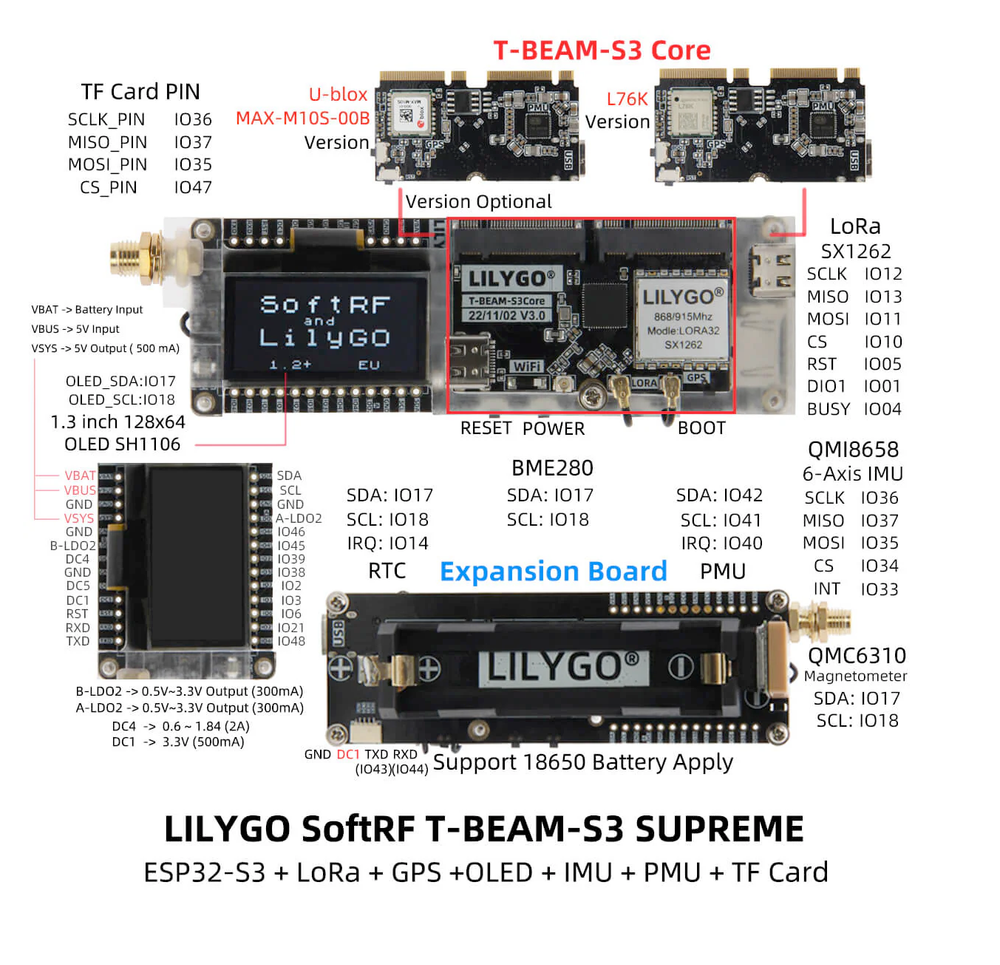

🚀 The LilyGo T-Beam Supreme is an advanced ESP32-S3-based development board designed for LoRa and GPS applications. It integrates an ESP32-S3 dual-core processor with WiFi and Bluetooth 5, offering seamless connectivity. ⚡

📡 Featuring an onboard LoRa transceiver (SX1262), the T-Beam Supreme supports long-range communication at 433/868/915 MHz. It also includes an upgraded Ublox GPS module for enhanced location tracking capabilities.

💾 The board is equipped with 16MB Flash and 8MB PSRAM, along with a 18650 Li-ion battery holder for portable applications, making it ideal for IoT, tracking, and telemetry projects.

Technical Specifications

Complete technical specification details for LilyGo T-Beam Supreme

Display

USB

Connectivity

Microcontroller

✨ Features & Pins

Quick Setup

Copy-paste configs for LilyGo T-Beam Supreme - auto‑generated from this board's exact hardware specs.

In Arduino IDE 2 select Lilygo T Beam Supreme from the esp32 by Espressif package. In PlatformIO use board = esp32-s3-devkitm-1. ESP32S3 · 240 MHz · 16MB · DIO.

In Arduino IDE 2, open Boards Manager, search "esp32" by Espressif and install it. Then go to Tools → Board and select "Lilygo T Beam Supreme" for the LilyGo T-Beam Supreme.

[env:lilygo_t_beam_supreme]

platform = espressif32

board = esp32-s3-devkitm-1

framework = arduino

; Exact hardware config for LilyGo T-Beam Supreme

board_build.mcu = esp32s3

board_build.f_cpu = 240000000L

board_build.flash_size = 16MB

board_build.flash_mode = dio

board_upload.flash_size = 16MBThe board value is a close generic match - check PlatformIO board registry for an exact fit.

esp32:

board: esp32-s3-devkitc-1

framework:

type: arduino # or "esp-idf"

# LilyGo T-Beam Supreme - 240 MHz ESP32S3

# Flash: 16MB | USB: USB-CPaste into your device's .yaml. See ESPHome ESP32 docs for full options.

esptool.py \

--chip esp32s3 \

--baud 921600 \

write_flash \

--flash_mode dio \

--flash_size 16MB \

0x0 bootloader.bin \

0x8000 partitions.bin \

0xe000 boot_app0.bin \

0x10000 firmware.binInstall: pip install esptool - replace firmware.bin with your binary - bootloader at 0x0

LilyGo T-Beam Supreme Pinout Diagram

Complete pin reference for LilyGo T-Beam Supreme

Safe Pins to Use

These pins are safe for general GPIO usage without boot or system conflicts

Why Are These Pins Safe?

Pins to Avoid or Use with Caution

Reserved for critical functions. Misuse may cause boot failures, programming issues, or system conflicts.

Boot behavior & flash voltage

Low-level debugging interface

USB Serial/JTAG communication

Memory & PSRAM connections

Debugging & firmware uploads

| PIN | Label | Why Avoid | Type |

|---|---|---|---|

| IO3 | GPIO3 | Sampled at reset to select JTAG interface (USB Serial/JTAG controller vs. external pins). Improper use can disable external JTAG or alter debug interface. | 🛠️ Strapping |

| IO10 | FSPICS0 | Used to select the external flash chip. It is required for flash access and cannot be repurposed without losing flash connectivity | ⚡ Flash |

| IO11 | FSPID | Used as a data line for flash (and in-package PSRAM). It should not be used as GPIO when the flash/PSRAM is in use. | ⚡ Flash |

| IO12 | FSPICLK | Drives the flash (and PSRAM) clock. This critical signal must be reserved for memory and not used as general GPIO. | ⚡ Flash |

| IO13 | FSPIQ | Used as a data line for flash/PSRAM transfers. Not available for other uses when flash/PSRAM is connected. | ⚡ Flash |

Useful Links

Datasheets and resources for LilyGo T-Beam Supreme

LilyGo T-Beam Supreme Custom Pin Mapping

Pin configuration and GPIO mapping for LilyGo T-Beam Supreme

| Pin | Function | ESP Pin | I/O Type | Description |

|---|---|---|---|---|

| 1 | 3V3 | 3.3V | POWER OUTPUT | 3.3V power output |

| 2 | GND | GND | POWER GROUND | Ground connection |

| 3 | 5V | 5V | POWER INPUT | 5V power input |

| 4 | IO1 | GPIO1 | BIDIRECTIONAL | GPIO, ADC, I2C |

| 5 | IO2 | GPIO2 | BIDIRECTIONAL | GPIO, ADC |

| 6 | IO3 | GPIO3 | BIDIRECTIONAL | GPIO, ADC |

| 7 | IO10 | SPI_CS | BIDIRECTIONAL | GPIO, SPI Chip Select |

| 8 | IO11 | SPI_D | BIDIRECTIONAL | GPIO, SPI Data |

| 9 | IO12 | SPI_CLK | BIDIRECTIONAL | GPIO, SPI Clock |

| 10 | IO13 | SPI_Q | BIDIRECTIONAL | GPIO, SPI Q |

| 11 | IO16 | LORA_CS | OUTPUT | GPIO, LoRa Chip Select |

| 12 | IO17 | LORA_RST | OUTPUT | GPIO, LoRa Reset |

| 13 | IO18 | LORA_IRQ | INPUT | GPIO, LoRa Interrupt |

| 14 | IO21 | GPS_TX | OUTPUT | GPS Module TX |

| 15 | IO22 | GPS_RX | INPUT | GPS Module RX |

| 16 | IO23 | BATTERY | INPUT | Battery Voltage Sense |

Default Tools & Configuration

Build and upload settings for LilyGo T-Beam Supreme

| Setting | Value |

|---|---|

| Bootloader tool | esptool_py |

| Uploader tool | esptool_py |

| Network uploader tool | esp_ota |

| Bootloader address | 0x0 |

| Flash mode | dio |

| Boot mode | qio |

| PSRAM type | opi |

| Maximum upload size | 3072 KB (3145728 bytes) |

| Maximum data size | 320 KB (327680 bytes) |

The LilyGo T-Beam Supreme uses esptool_py for uploads , esp_ota for OTA updates, and esptool_py bootloader at 0x0.

Flash mode: dio | Boot mode: qio | PSRAM: opi

Max sketch size: 3072 KB | Max data size: 320 KB

Similar Boards

Other development boards with ESP32S3 microcontroller

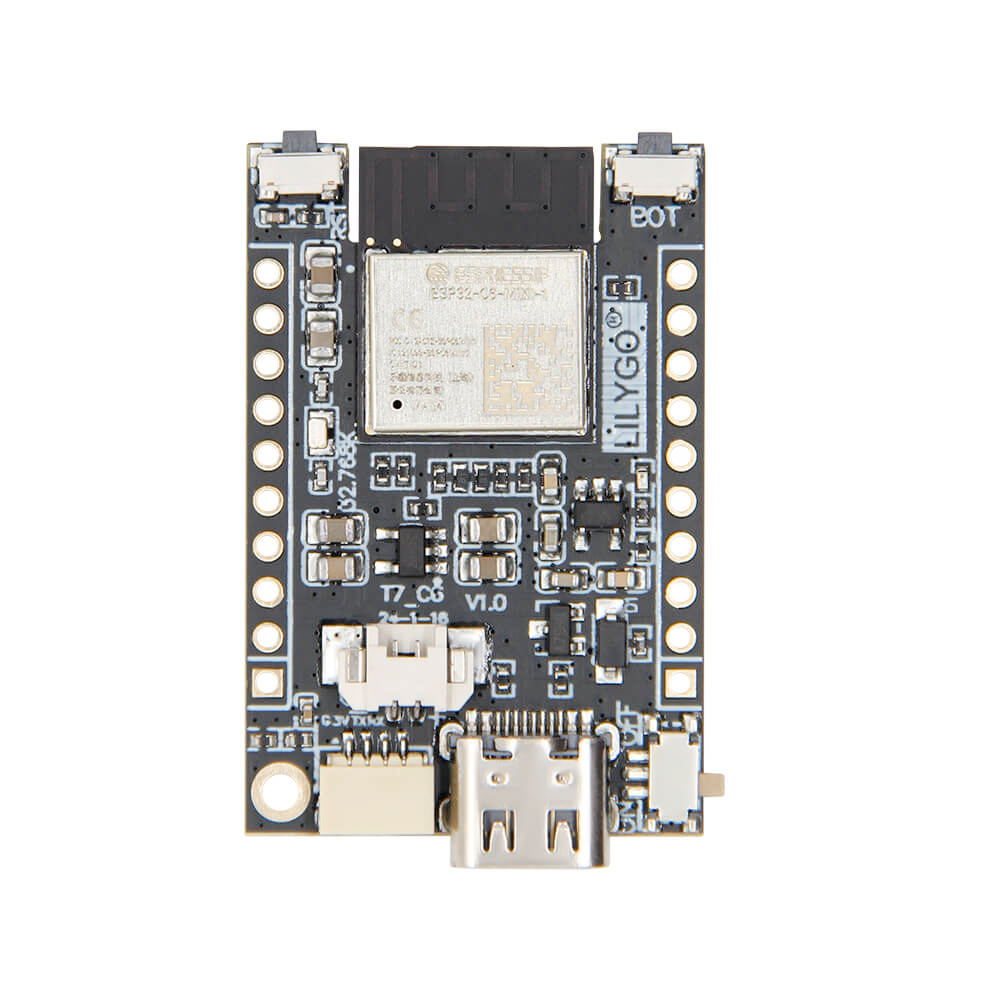

LilyGO T7-C6

LilyGO T7-C6 development board is based on esp32c6 microcontroller and uses riscv32 architecture.

LilyGo TTGO T-Display 1.14 Inch LCD ESP32

LilyGo TTGO T-Display 1.14 Inch LCD ESP32 development board is based on esp32 microcontroller and uses xtensa...

TTGO T-Call (LilyGO)

TTGO T-Call (LilyGO) development board is based on esp32 microcontroller and uses xtensa architecture.